产品中心

产品中心

P产品分类RODUCT CATEGORY

逻辑分析仪LAP-C(162000+)内部采样率:100Hz~200MHz,内存容量:64Mbits,每信道内存深度:2Mbits触发通道 :16CH。PC-Based接口,USB1.1(2.0)传输供电,采用业界Smart+软件在操作与设定更加贴近使用者,加速设定流程,方便使用者『直觉式』操作,提供状态信号输出,可搭配其它仪器使用。如:示波器。

产品型号:LAP-C(162000+)

产品型号:LAP-C(162000+) 厂商性质:代理商

厂商性质:代理商 更新时间:2024-07-01

更新时间:2024-07-01 访 问 量:3270

访 问 量:3270 立即咨询

立即咨询

联系电话:021-51087863

联系电话:021-51087863

逻辑分析仪LAP-C(162000+)主要特点:

内部采样率:100Hz~200MHz

.内存容量:64Mbits

.每信道内存深度:2Mbits

.触发通道 :16CH

.PC-Based接口,USB1.1(2.0)传输供电

.采用业界Smart+软件在操作与设定更加贴近使用者,加速设定流程,方便使用者『直觉式』操作

.提供状态信号输出,可搭配其它仪器使用。如:示波器.

通用免费总线-

1-WIRE、CAN 2.0B、IRDA、3-WIRE、JTAG 2.0、PS/2、I2C(EEPROM 24LCS61/24LCS62)、SSI Interface、MANCHESTER、MILLER、SPI Compatible(Atmel Memory)、I2C、UART(RS-232C/422/485)、SPI、7-SEGMENT LED、USB 1.1、LCD1602、DIGITAL LOGIC、ARITHMETICAL LOGIC、MICROWIRE、I2C(EEPROM 24L)、UP DOWN COUNTER、MICROWIRE(EEPROM 93C)、LIN 2.1、LED Pitch Array、通用免费总线

不支持- MCU-51 DECODE、PCI、Compact Flash 4.1、USB 2.0、RGB Interface、SD3.0、eMMC

逻辑分析仪LAP-C(162000+)技术参数:

【 产品规格 】 | |

| 采样率 | 内部(时序)(异步) 100Hz~200MHz 外部(状态)(同步) 100MHz |

| 待测信号 | 带宽 75MHz 触发电压范围 -6V~+6V 触发电压分辨率 ±0.1V |

| 内存 | 内存容量 64Mbits 每信道内存深度 2Mbits (Max 512Mbits for compression) |

| 触发 | 触发方式 Pattern/Edge 触发通道 16 CH 延后触发 YES 触发阶层 1 Level 触发计数 1~65535 |

| 软件功能 | 波形数据压缩 Max 2M bits x 256 时基范围 5ps~10Ms 波形垂直缩放比例 1~5.5 操作接口 中文(繁/简)英文 波形触发分页大值 8192页 触发标示 波形宽度显示 讯号滤波及滤波延迟 波形触发延迟 可增加定位棒 定位棒自动贴进功能 软件自动升级 可选择分析数据的范围 资料统计 自动存档 滤波间隔棒 总线分析 数据比对 总线Latch功能 总线封包列表功能 封包列表汇出功能 *总线协议触发 : 串并列 *脉波宽度触发模块: 选购 |

| 电源 | 电源USB (DC 5V, 500mA) 静态消耗功率 1W 瞬间大消耗功率 2W |

| 其它 | 系统支持Windows 2000 / XP(32bits) / Vista / Win 7 相位误差 < 1.5ns 大输入电压 ±30V 输入阻抗 500KΩ/10pF 安规认证 FCC / CE |

| 堆栈功能 | 不支援 |

| Double模式 | 支援 通道: 16通道 内存容量: 4M |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||

| 具有外部按钮执行逻辑分析仪采样功能 |

| 在孕龙逻辑分析仪的硬件上,有一个START的按钮,当逻辑分析仪软件在开启的状态,可利用此按钮来让逻辑分析仪执行取样的动作。此按钮能让您更快速的操作逻辑分析仪取得被测物的资料。 |

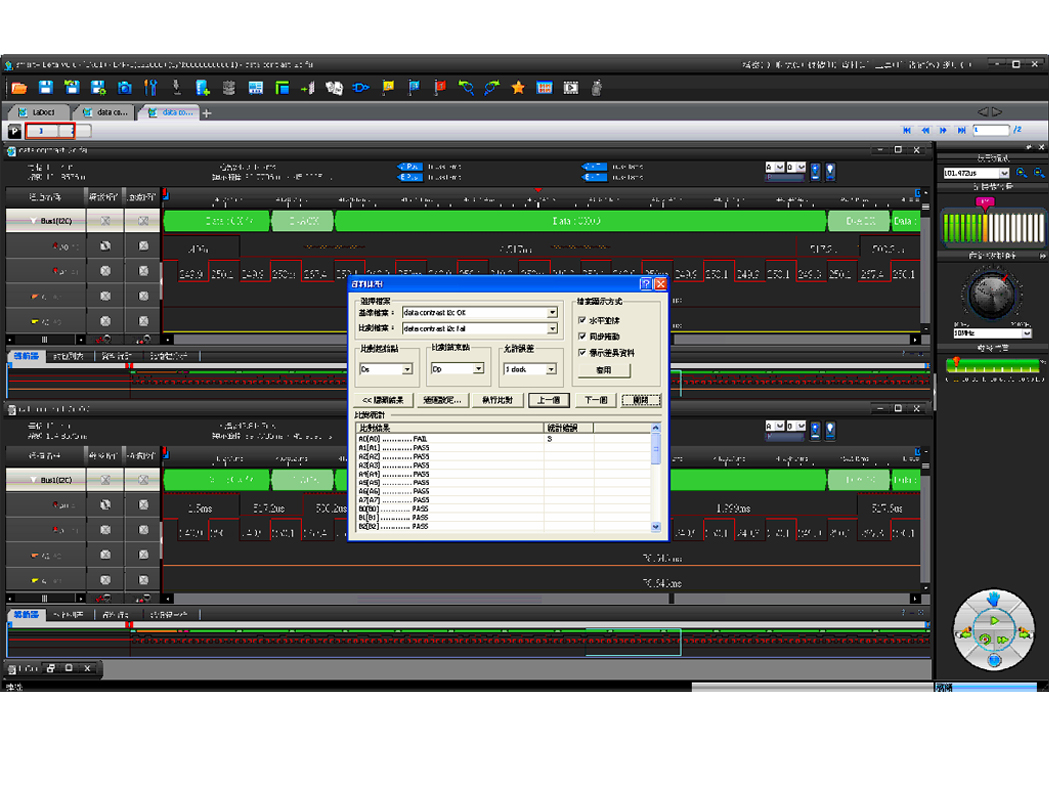

| 资料对比 |

| |||

| 利用数据比对功能可将两个LA存盘进行波形比对,数据比对功能会自动将两笔存盘内波形差异点以橘红色引号来标示,将备份文件取出与现状档案做Data Compare的动作,迅速找出问题点,不用再Step Into慢慢查找。 | |||

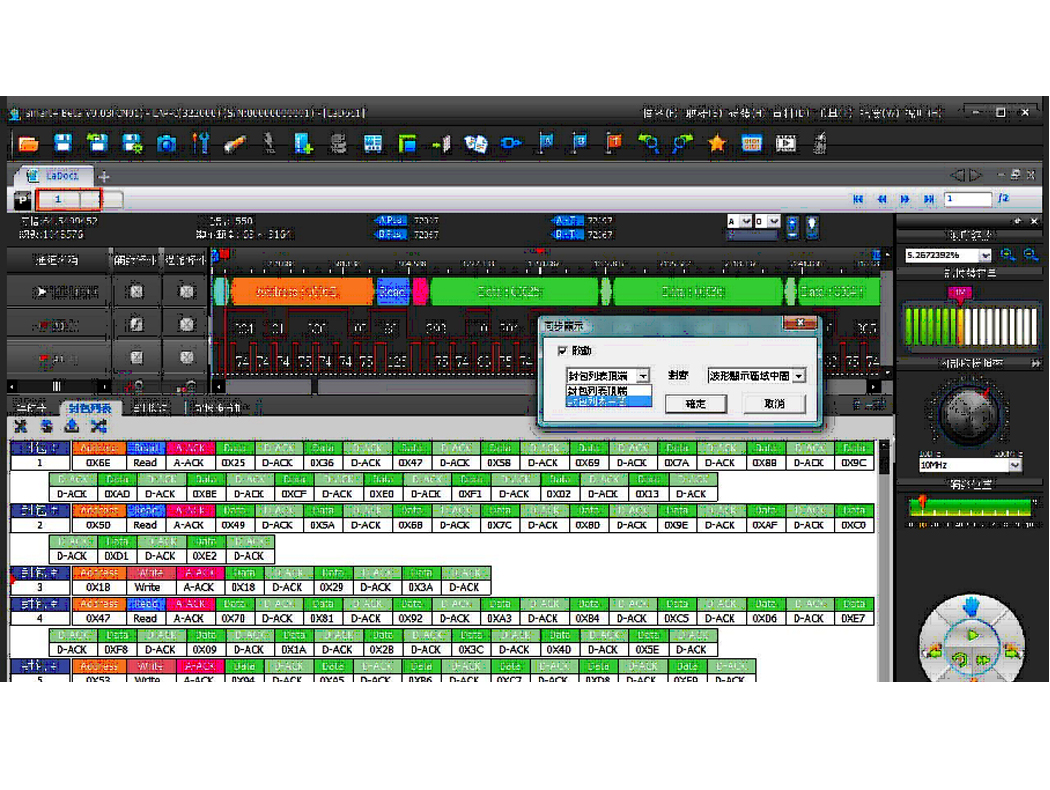

| 总线封包列表 |

|  | ||

| Smart+ 快速的总线译码,让工程师可以快速的了解串行协议信号信息,其*的总线封包列表功能,更可将庞大的封包资料以树状直列方式显示于列表中,让工程师更快速的分析各个封包状态前后关系。这对于程序验证、观察、Drives初始化动作,有着显着的帮助。 | |||

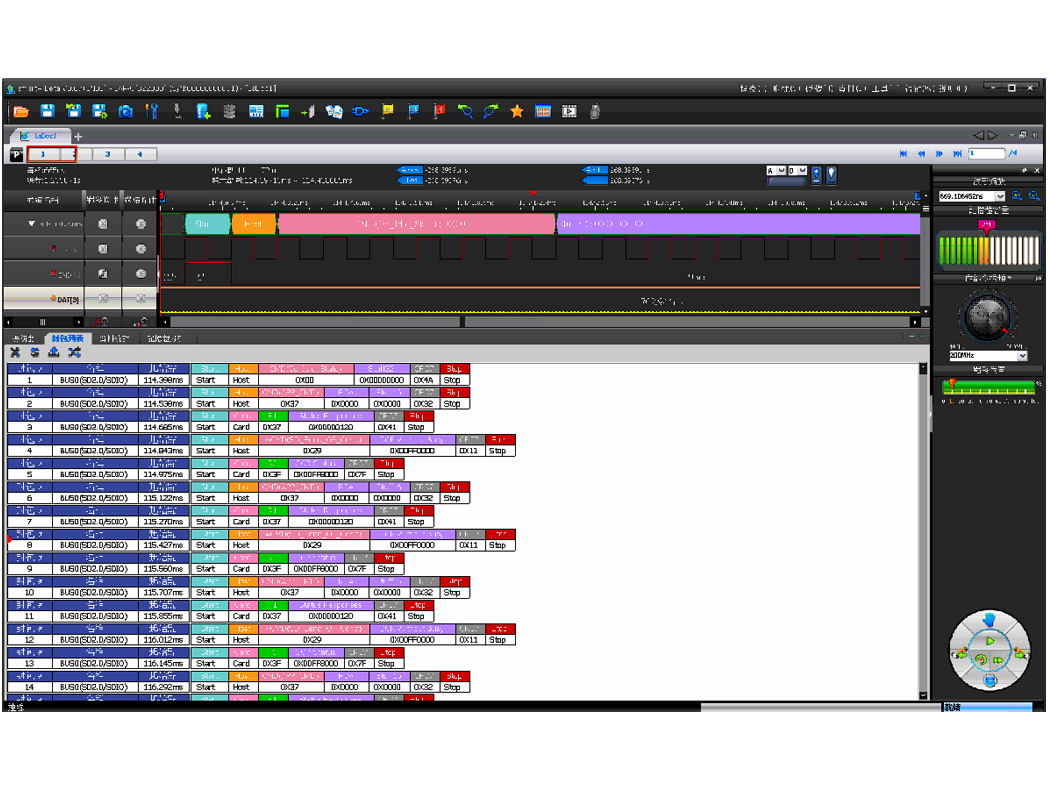

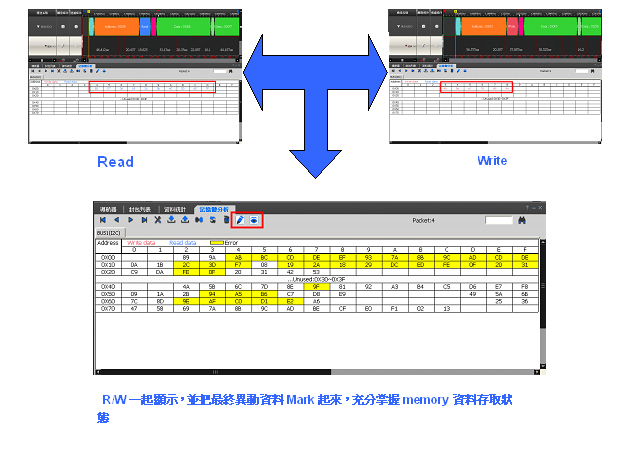

| 内存分析 |

| |||

| Smart+具备将总线译码模块所解析后的封包数据,仿真成内存中常见的memory map来进行显示。主要分析EEPROM内存内各地址的读写状态及异常显示,可以帮助工程师加速掌握内存动作行为。 此功能不仅仅只是纪录,每个封包是读是写也可单独分析,更能显示后内存每个地址的异动状态,使工程师能快速的除错验证与比对分析数据,加速项目的进行。 | |||

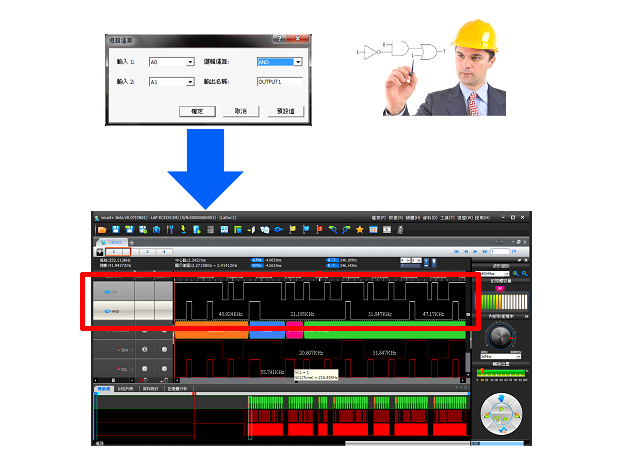

| 逻辑运算 |

| |||

| 使用者只需点选icon,即可设定信号信道中任意两组作为逻辑运算输入,经由Smart+快速计算逻辑输出状态并同步显示于波形显示区内,方便工程师在设计电路中,仿真计算数字信号所产生的讯号结果。Smart+所支持的逻辑闸AND、OR、NAND、NOR、XOR、XNOR及NOT等。 | |||

孕龙du家的影像解析功能,是专门为有显示类别的总线模块而设计(如:CMOS Image、7-SEGMENT LED、LCD12864、LCD1602..等)。当工程师使用Smart+撷取到影像数字信号后,透过影像解析功能可把当下的影像信号还原成图片或者多张显示,省去需要观看满满的数值数据时间,直接查看还原图,更快便能掌握数据是否错误,以更直觉式、更具全面性的新型态量测方式,协助工程师做验证。

| I2C总线实际量测–步骤一 : |

| 将测试线连接至逻辑分析仪讯号连接座上,将测试线另外一端连接至待测物上,依照待测物状况不同,也可以使用配件内的测试钩来连接待测物。 |

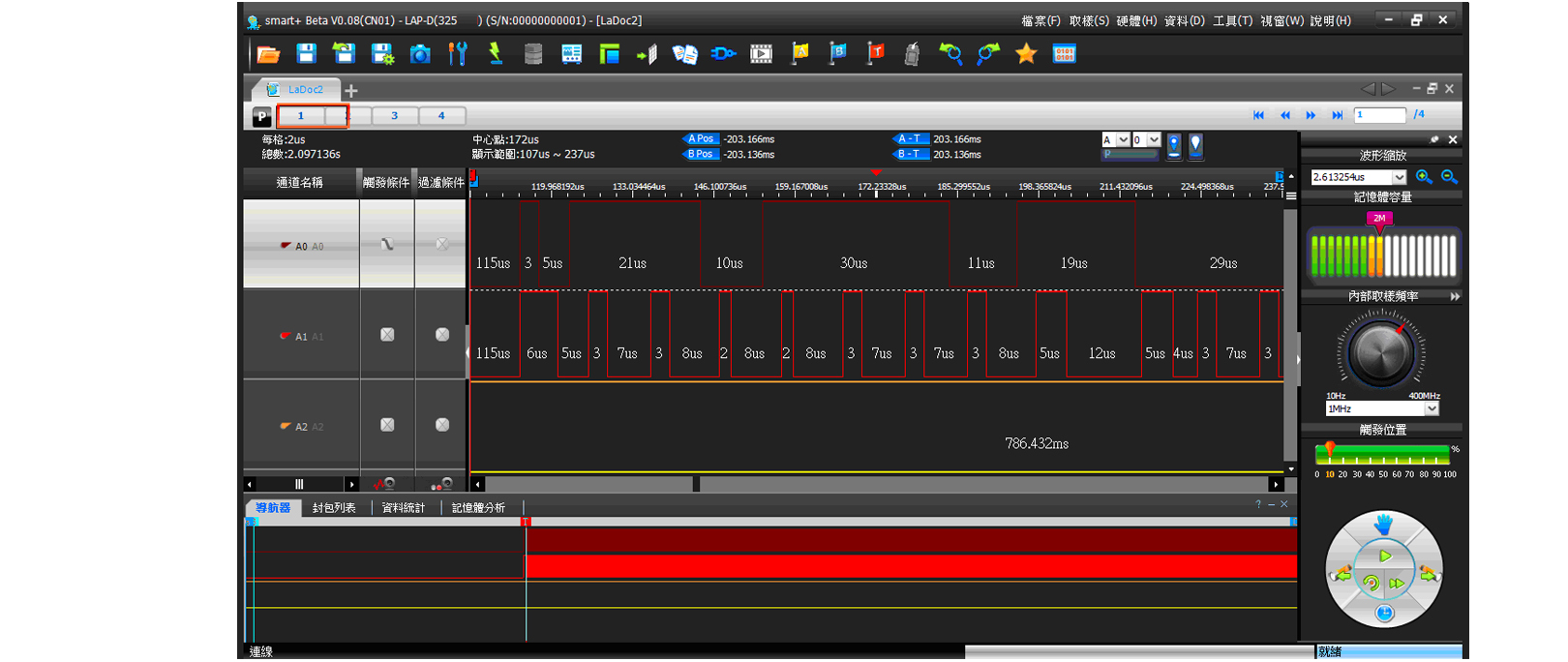

| 步骤二 |

| |

| 依照快速安装手册第三章所述,进行逻辑分析仪设定,设定完成后启动逻辑分析仪软件及送出待测物讯号进行撷取,撷取完成如图所示。 提示:逻辑分析仪取样率需高过待测目标频率四倍以上才能确保讯号正确。 |

| 步骤三 总线精灵 |

| |

| 直接一动鼠标并点击信道名称叫出总线精灵,即可将讯号归纳成总线,设定选项有三项一般信道、总线以及总线协议,在总线协议中直接在搜寻键入总线关键词即可快速查找出总线协议。 |

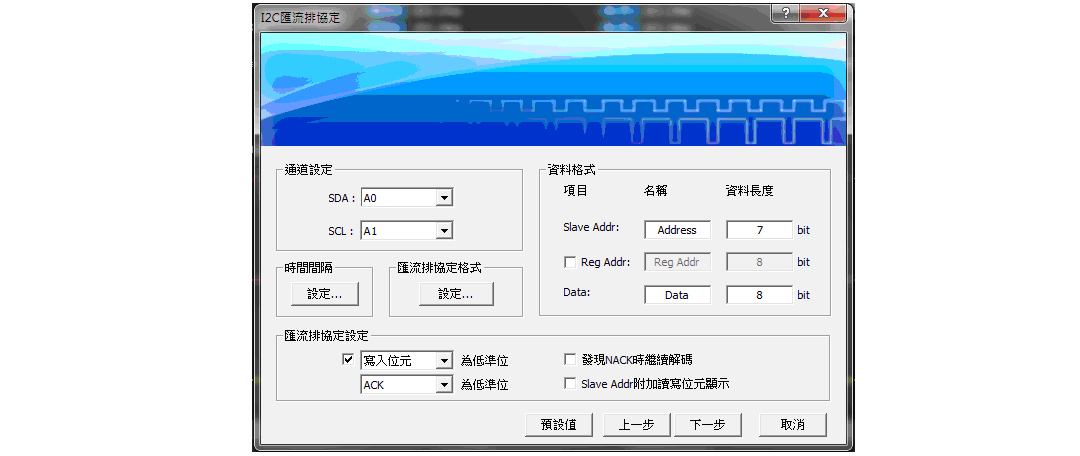

| 步骤四 总线属性 |

| |

| 在步骤三确认总线协议后按下下一步,便会直接进入总线属性,确认脚位以及参数数据便完成整个总线协议的设定。 提示:每一种总线分析模块均有相对应的参数设定,使用者可在参数设定中依照待测总线内容加以设定。 |

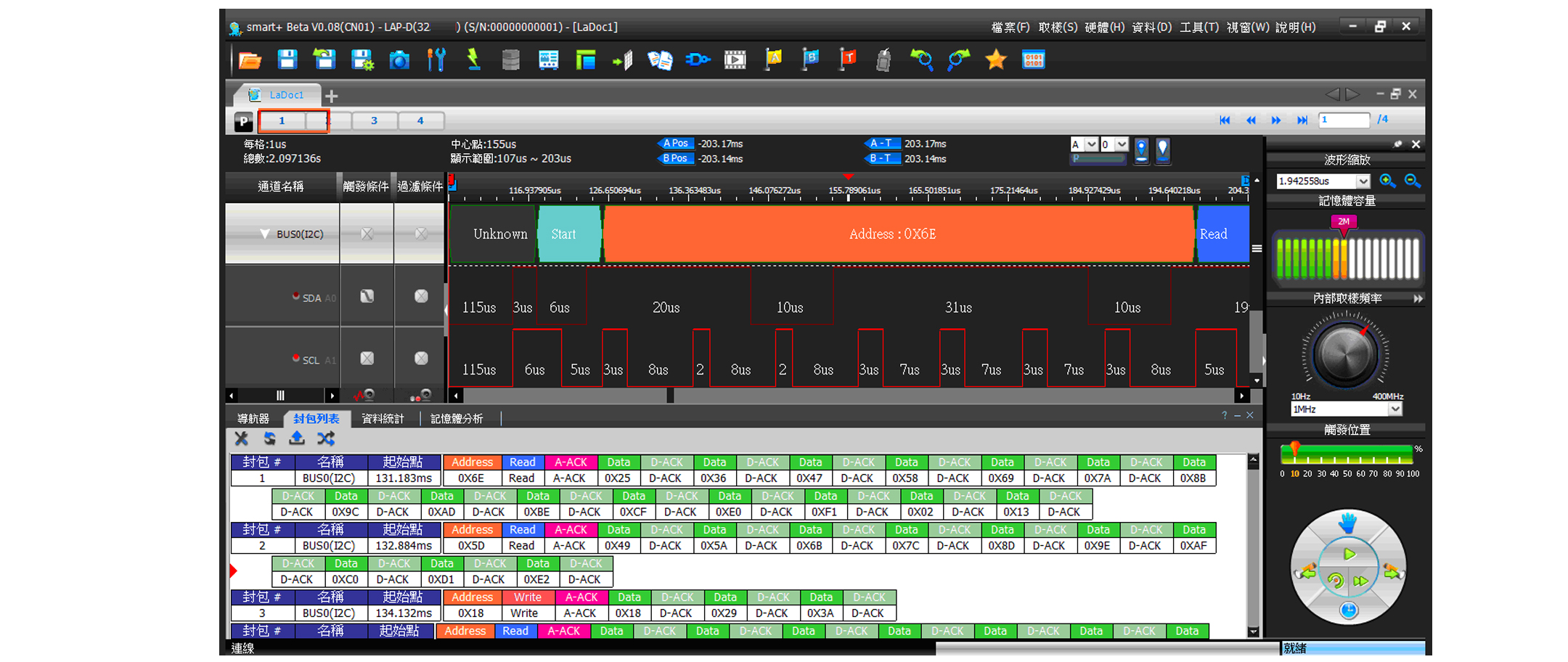

| 步骤五 |

| |

| 完成设定后,软件模块会将总线内的封包数值显示于屏幕上。 提示:孕龙科技逻辑分析仪软件还有其它强大功能可帮助使用者进行总线分析,如封包列表显示、数据搜寻、脉波宽度搜寻….等等。 |

物品清单

主机,测试线,测试勾,USB线,软件/说明书光盘,保修卡,携带包各壹套。