产品中心

产品中心

P产品分类RODUCT CATEGORY

孕龙逻辑分析仪 LAP-C322000内部取样频率:100Hz~200MHz,内存容量:64Mbits,每信道内存深度:2Mbits,触发通道 :32CH,PC-Based界面,采USB1.1(2.0)传输供电总线协议触发:串行 / 并行。

产品型号:LAP-C322000

产品型号:LAP-C322000 厂商性质:代理商

厂商性质:代理商 更新时间:2024-07-01

更新时间:2024-07-01 访 问 量:2540

访 问 量:2540 立即咨询

立即咨询

联系电话:021-51087863

联系电话:021-51087863

孕龙逻辑分析仪 LAP-C322000介绍:

孕龙逻辑分析仪 LAP-C322000支持I²C、SPI、USB2.0、RS232、CAN、LIN、FlexRay、MIL-STD 1553、I²S常用的几个总线协议,还支持MVB、WTB、GPIB、PCI、USB 1.1、USB 2.0、HDMI、I2S、S/PDIF、BMS、ModBus等110种总线协议而且全部免费!!!!!!

【 产品规格 】 | |

| 取样频率 | 内部(时序)(异步) 100Hz~200MHz 外部(状态)(同步) 100MHz |

| 待测信号 | 频宽 75MHz 触发电压范围 -6V~+6V 触发电压分辨率 ±0.1V |

| 内存 | 内存容量 64Mbits 每信道内存深度 2Mbits (Max 512Mbits for compression) |

| 触发 | 触发方式 Pattern/Edge 触发通道 32 CH 延后触发 YES 触发阶层 1 Level 触发计数 1~65535 |

| 软件功能 | 波形数据压缩 Max 2M bits x 256, 可用通道24CH 时基范围 波形垂直缩放比例 操作接口 波形触发分页大值 波形宽度显示 波形滤波及延迟 波形触发延迟 可增加定位棒 定位棒自动贴进功能 软件自动升级 可选择分析数据的范围 资料统计 自动存档 波形滤波分隔棒 总线分析 数据比对 总线Latch功能 总线封包列表功能 封包列表汇出功能 *总线协议触发: 串行 / 并行 *脉波宽度触发模组 |

| 电源 | 电源USB (DC 5V, 500mA) 静态消耗功率 1W 瞬间大消耗功率 2W |

| 其它 | 系统支持 Windows 2000 / XP (32bits)/ Vista / Win 7 相位误差 < 1.5ns 大输入电压 ±30V 输入阻抗 500KΩ/10pF 安规认证 FCC / CE / WEEE / RoHS /REACH |

| 堆栈功能 | 支持 Channel mode: LAP-C(322000) + LAP-C(322000) => Channel = 62CH, Memory = 2Mbits Memory mode: LAP-C(32128) + LAP-C(32128) => Channel = 31CH, Memory = 256Kbits |

| Double模式 | 支持 通道: 16通道 内存容量: 4M |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||

物品清单

主机,测试线,测试勾,USB线,软件/说明书光盘,保修卡,携带包各壹套。

| 具有外部按钮执行逻辑分析仪取样功能 |

| 在孕龙逻辑分析仪的硬件上,有一个START的按钮,当逻辑分析仪软件在开启的状态,可利用此按钮来让逻辑分析仪执行取样的动作。此按钮能让您更快速的操作逻辑分析仪取得被测物的资料。 |

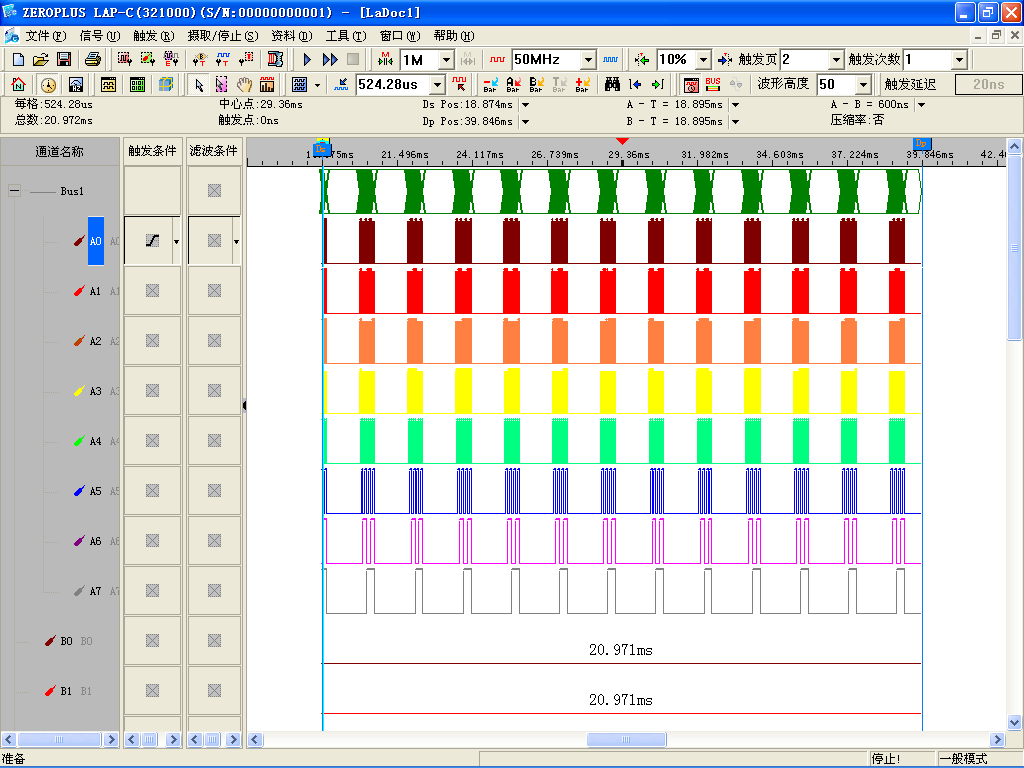

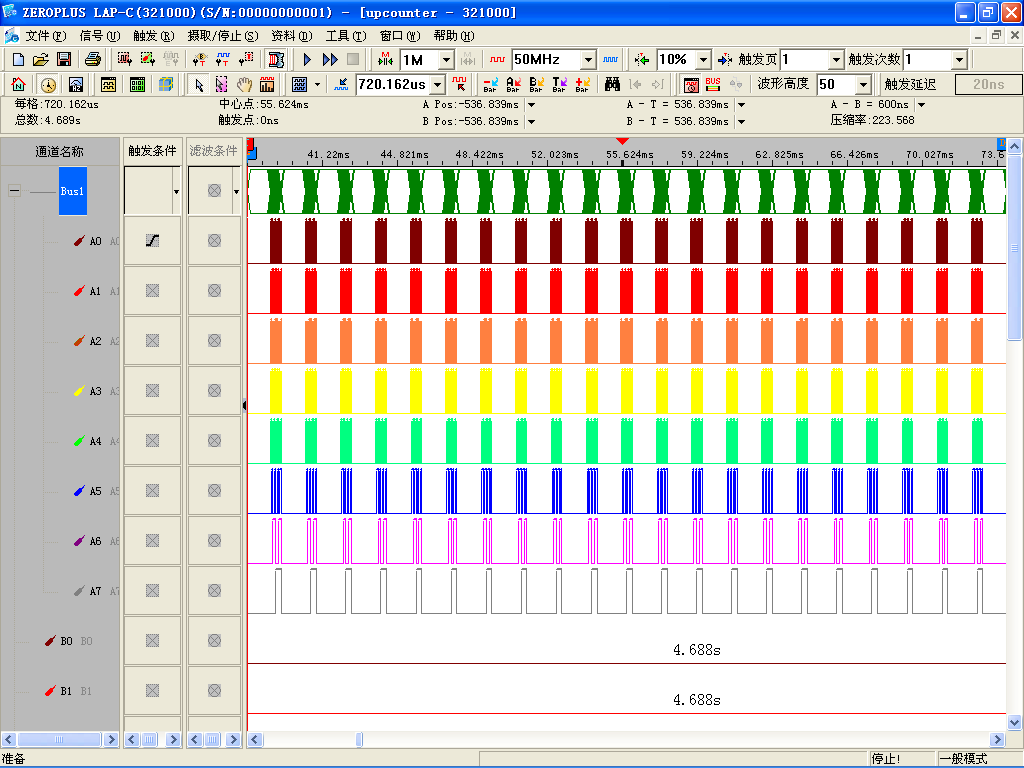

| 压缩技术 |

|  | ||

| 孕龙科技推出波行压缩zhuan利技术,可以在不增加内存的状况下获取更长的波形资料。For Example:设定内存深度为1M,取样率为50MHz。未开启压缩功能时仅可撷取20.972ms,若开启压缩功能后,以同样记忆深度为1M,取样率为50MHz进行取样,则可以将波形时间增加至3.999s,大大的提升了撷取数据量。 | |||

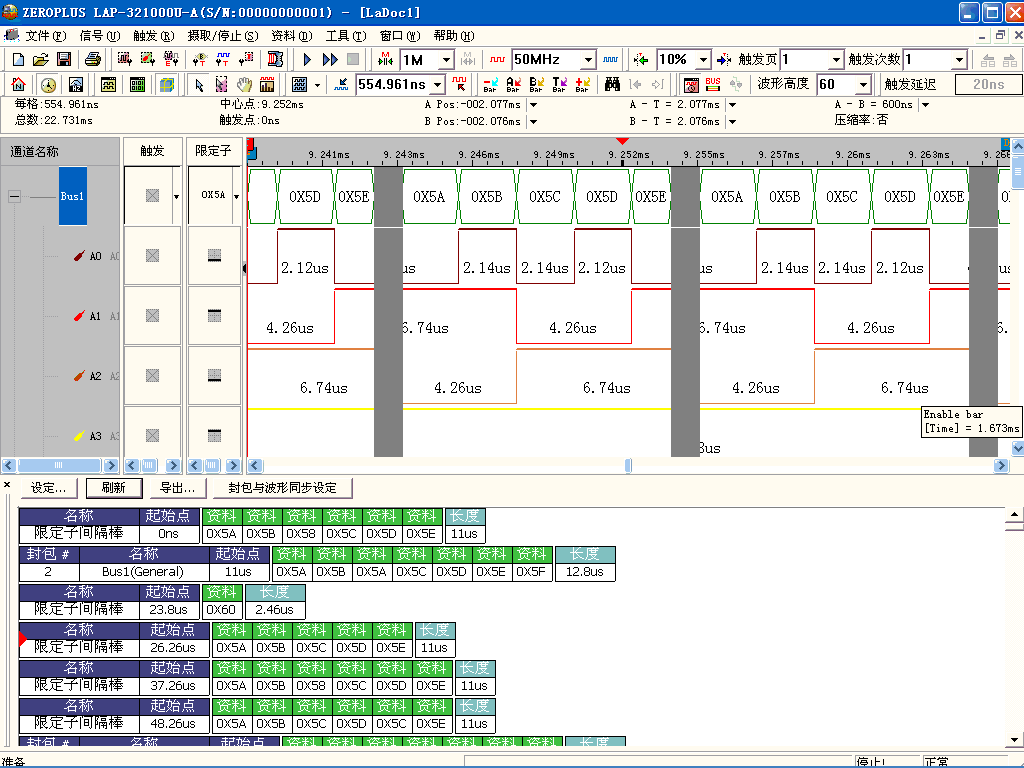

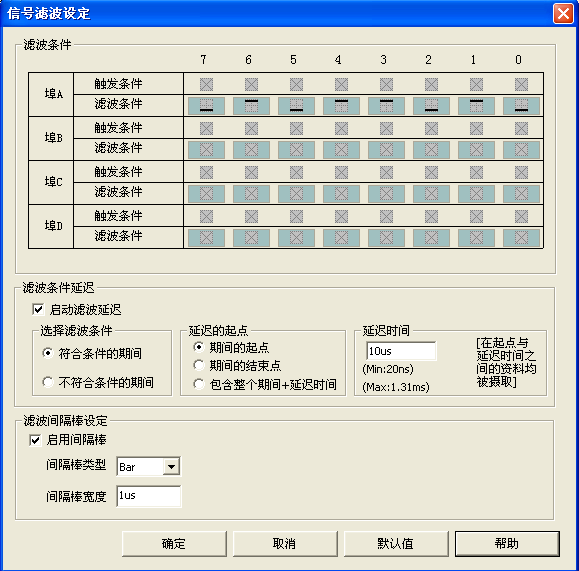

| 信号滤波延迟 |

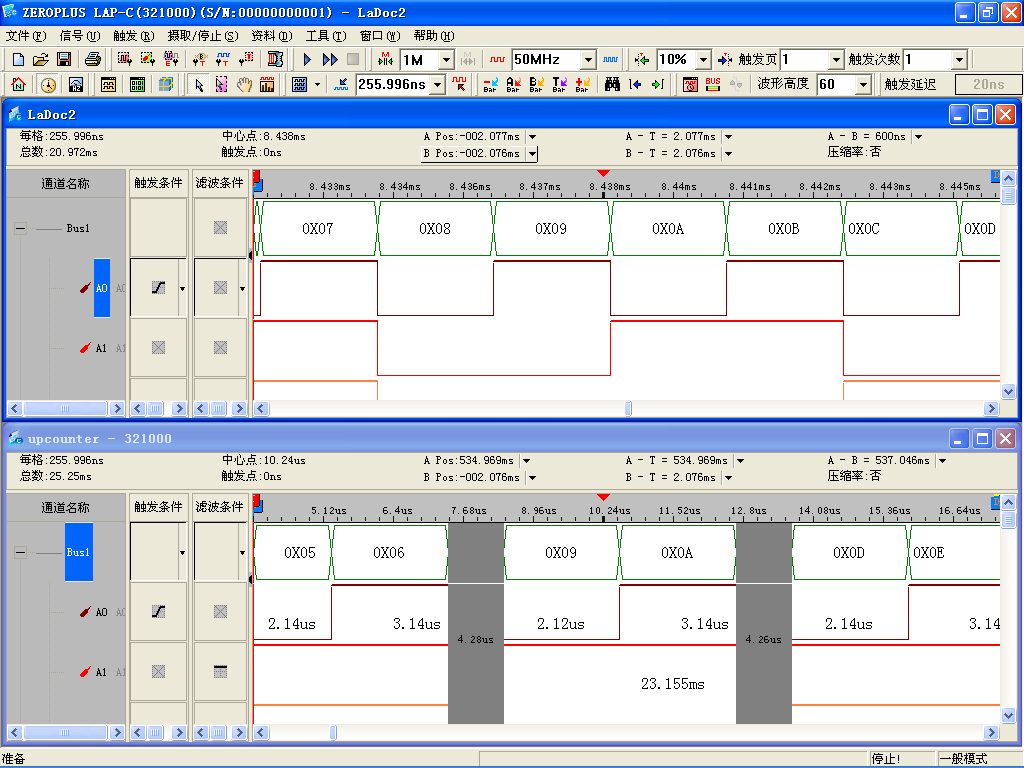

|  |  | |

| 孕龙科技推出了信号滤波延迟zhuan利技术,信号滤波功能可以将讯号进行条件式的撷取,如下图所述,将A1通道设定滤波条件为高准位,透过上下并列窗口的比较可明显看出两者间的差异,而信号滤波延迟则是能够将信号滤波的条件更加灵活化,使用者可自行设定过滤的时间状态。 For Example:客户端有一组DUT出现Bug,Bug的内容是当程序读取的时候可能会出现读取错误的情况,此时就可以利用信号滤波延迟进行条件式的撷取,藉此进行Bug分析 (读取状态为0X5A、读取命令周期为10us)透过信号滤波延迟功能,逻辑分析仪就可以只针对当0X5A的数值出现后仅撷取命令时间10us,进而分析Bug的发生问题。 | |||

| 触发分页技术 |

|  | ||

| 孕龙逻辑分析仪加入了触发分页(Trigger Page)的zhuan利技术,Trigger Page简单的说就是将连续又漫长的讯号数据分页。 以目前所设定的内存长度为一页,触发点的所在即为*页,分析完*页的数据后,只要被测物的数据每一次都是相同的,且触发状态设定不变,就可以将Trigger Page设为2再重新启动逻辑分析仪,待逻辑分析仪停止撷取数据且完成显示时,波形显示区内的内容即为第二页的数据,第二页的数据就是紧接着*页结束后的数据。 For Example:设定记忆深度为32K、取样率为200MHz,设定触发分页为1,所撷取讯号的结束点为147.465us,而数据为0X47的前半段,再以相同记忆深度与取样率进行撷取,设定触发分页为2时,所撷取讯号开始点为触发分页1时的结束点147.465us,此时可看见资料0X47的后半段。 | |||

| 触发次数计算 |

|  | ||

| 孕龙逻辑分析仪加入了触发次数计算(Trigger Counter)的技术,Trigger Counter,的功能是将有一个以上符合触发值的被测信号,使用者可决定触发点是要在第几个符合触发设定的位置进行触发, *次碰到触发的设定状态时就触发Trigger Counter就要设定为1(预设),第三次碰到触发的设定状态时才触发Trigger Counter就要设定为3,依此类推。 | |||

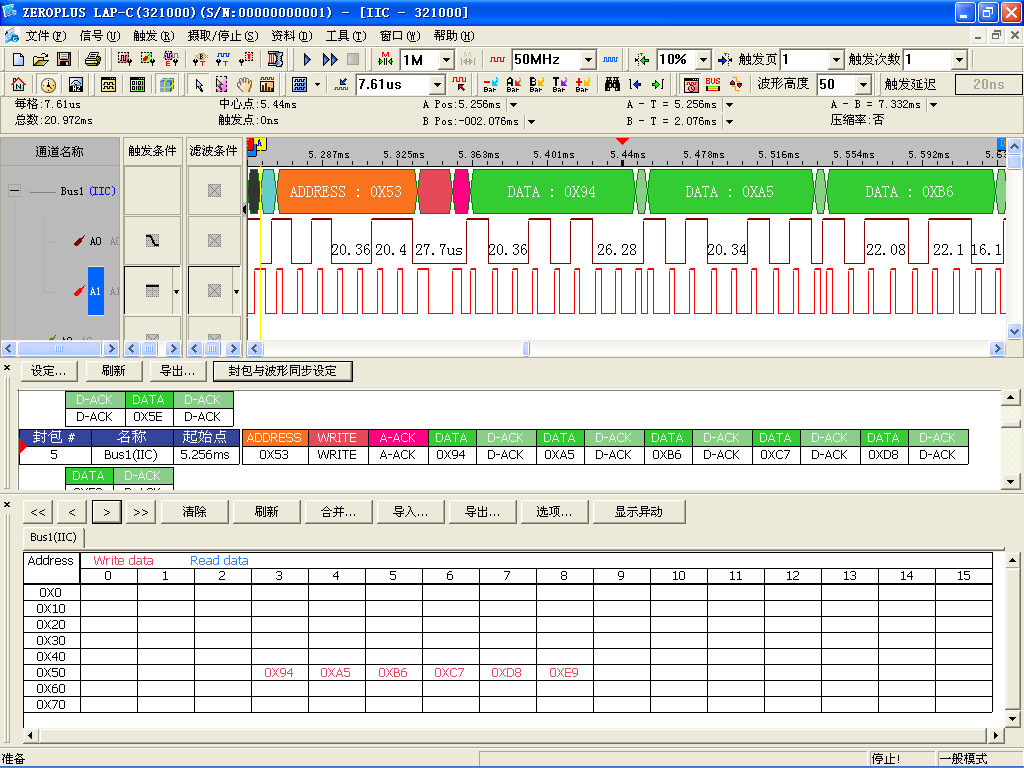

| 内存分析 |

| |||

| 孕龙逻辑分析仪加入了内存分析功能(Memory Analyzer),针对总线中有使用ADDRESS的类别,如IIC、HDQ、3-WIRE、PM、SM、IIC(EEPROM 24LX)…等等,能够将总线中的ADDRESS、READ/WRITE、DATA状态记录于内存分析表中,让使用者进行总线分析时也能够针对ADDRESS、READ/WRITE、DATA加以记录分析。 | |||

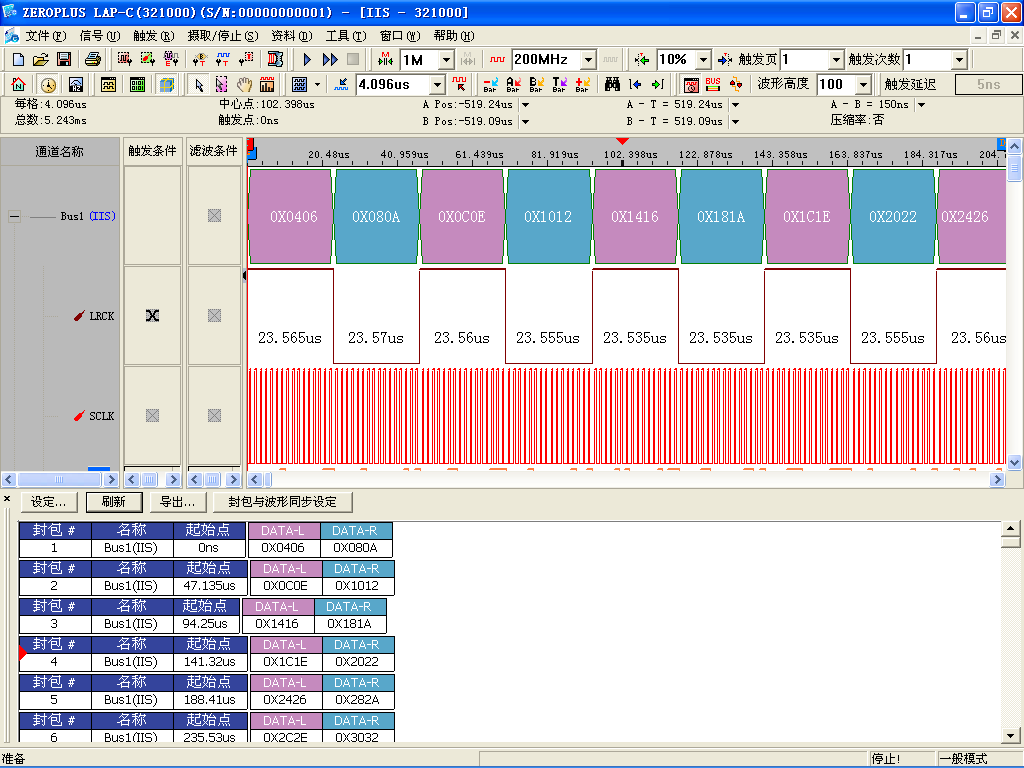

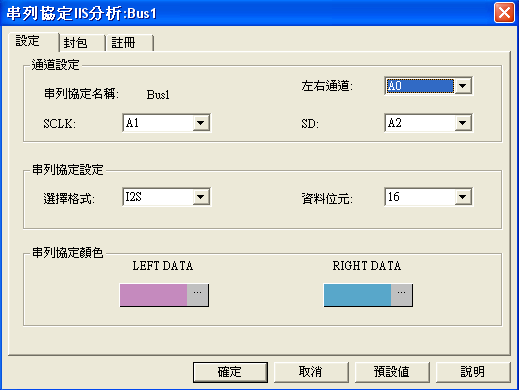

| 总线协议分析实例 – IIS总线协议分析译码 |

|  | ||

| 孕龙科技的I2S总线分析模块,可帮助使用者进行I2S总线分析,透过译码模块可将讯号中的Data-L及Data-R数值直接显示于屏幕上,孕龙科技IIS总线分析模块可依照待测I2S讯号格式让使用者选择Data bit长度为16、20、24、32 bits,方便使用者面对各种不同的I2S讯号均能顺利分析。 | |||

| IIS总线实际量测–步骤一 |

| 将测试线连接至逻辑分析仪讯号连接座上,将测试线另外一端连接至待测物上,依照待测物状况不同,也可以使用配件内的测试钩来连接待测物。 |

| 步骤二 |

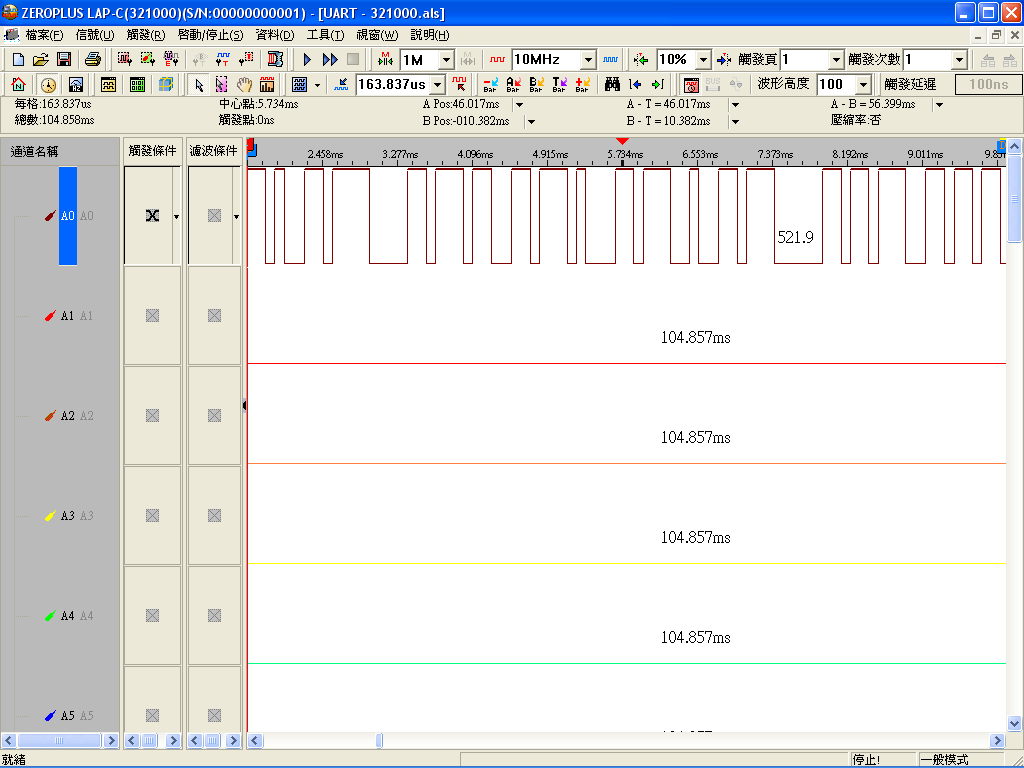

| |

| 依照快速安装手册第三章所述,进行逻辑分析仪设定,设定完成后启动逻辑分析仪软件及送出待测物讯号进行撷取,撷取完成如图所示。 提示:逻辑分析仪取样率需高过待测目标频率四倍以上才能确保讯号正确。 |

| 步骤三 |

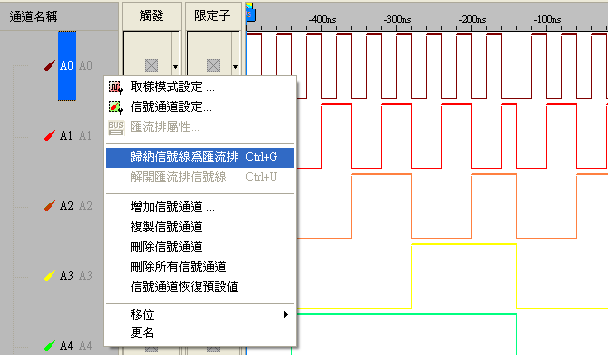

| |

| 将讯号归纳成总线,按住键盘上的CTRL键不放,在信道列表上以鼠标点选要归纳的讯号信道使其反白,选择完毕后点下鼠标右键选择归纳信号为总线选项,此时信道列表内会增加一组所设定的总线。 提示:进行总线分析时,需依照待测Protocol信道数来设定总线信道数,如IIC便设定两个通道,UART设定一个通道。 |

| 步骤四 |

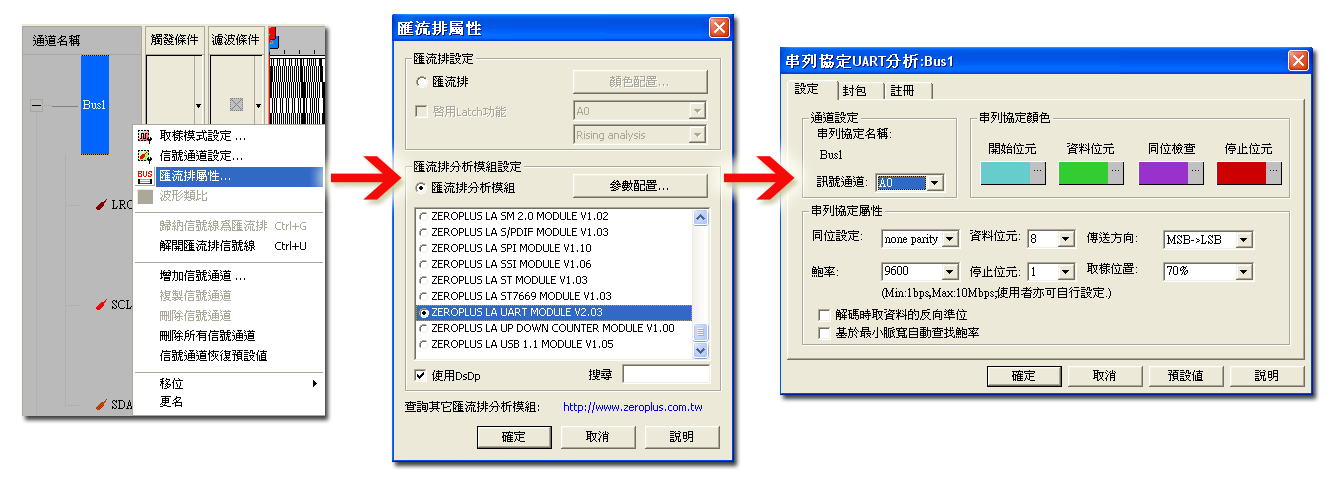

| |

| 在新增的总线上点选鼠标右键,选择总线属性,再选择要使用的总线分析模块。 提示:每一种总线分析模块均有相对应的参数设定,使用者可在参数设定中依照待测总线内容加以设定。 |

| 步骤五 |

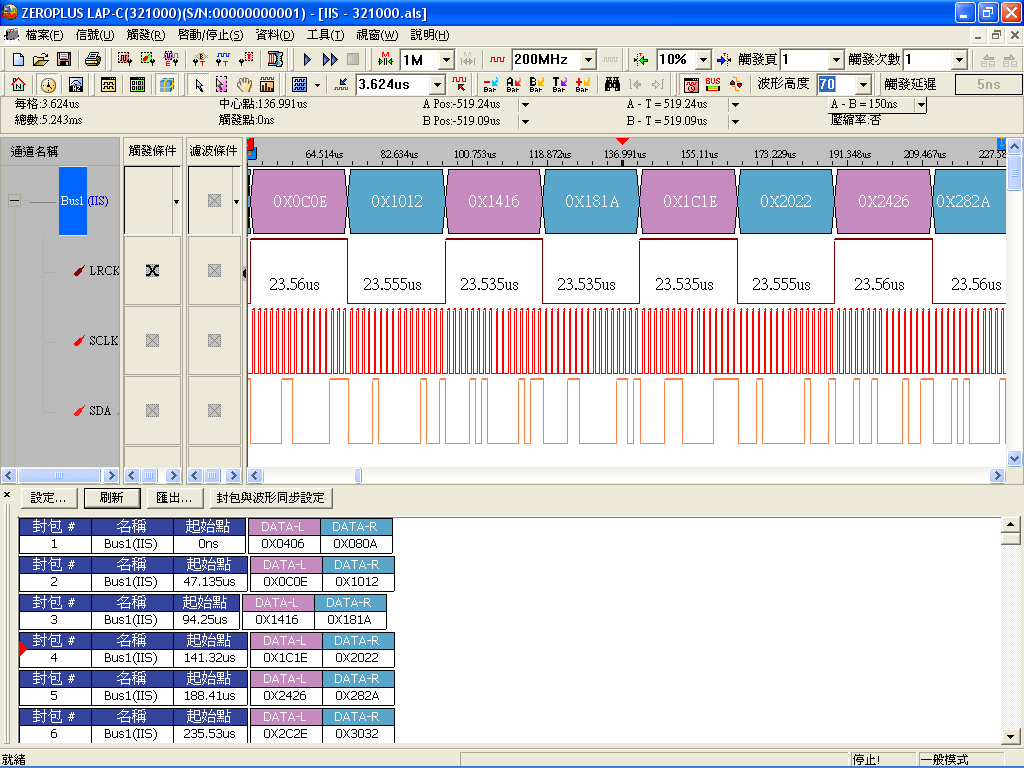

| |

| 完成设定后,软件模块会将总线内的封包数值显示于屏幕上。 提示:孕龙科技逻辑分析仪软件还有其它强大功能可帮助使用者进行总线分析,如封包列表显示、数据搜寻、脉波宽度搜寻….等等。 |